こんにちは、ドルフィンシステムの笹生です。

今回は 「USRP-2954 のベースの処理遅延時間を計測」してみたご報告です。

SDR 機器は受信の場合、大体 RF の回路からアナログベースバンド信号にダウンコンバートし、ADコンバータでサンプリング後 IQ のデジタルベースバンドデータになることで、その後のデジタル信号処理をすることになります。

また送信の場合は、デジタル信号処理をして IQ デジタルバースバンドデータになった信号を DAコンバータでアナログベースバンド信号にし、RFにアップコンバートして送信することになります。

(この説明はあくまでざっくりですが図にすると下図のような感じです)

さてRF信号が入ってから、デジタルベースバンド信号になるまで、その逆について処理時間が当然のことながらあると思います。

受信した復調データを基に応答 (Ack等)を送信するなど、双方向でのやり取りがあることも多いと思いますが、タイムアウトしてしまうほど時間がかかるようだとそもそも問題があります。

そこで今回は弊社で開発した簡易的な遅延差測定ツールを使って USRP-2954 での処理遅延時間を計測してみたいと思います。

USRP-2954 の処理遅延を計測してみる

USRP-2954 の処理遅延を計測するにあたって以下のような系で計測しました。ケーブル長はそれぞれ 1m です。ケーブル自体の経路差は数ns だと思います。

簡易遅延計測ツールは 100ns 単位で計測できます。

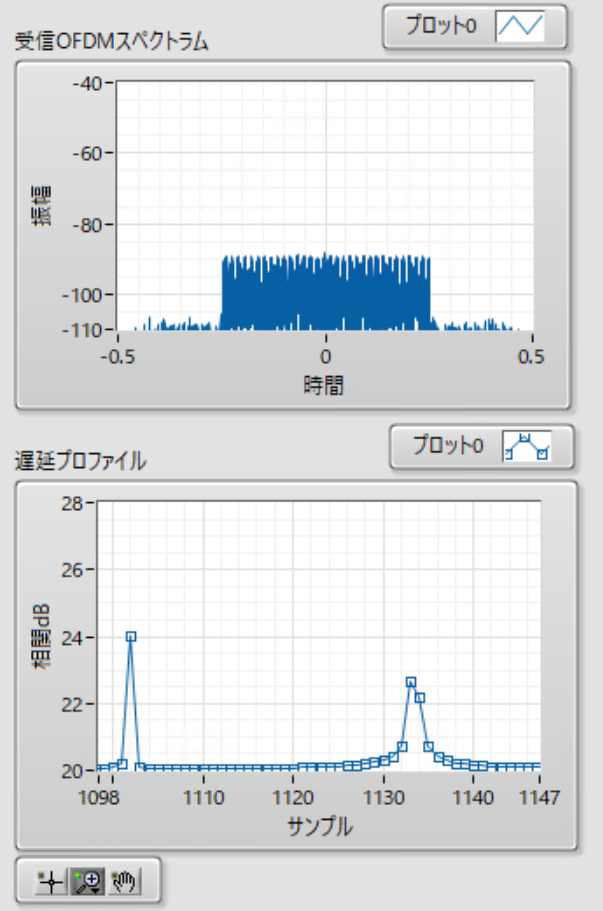

横軸の差 * 100ns が受信→送信の処理遅延に相当します。

このケースは IQレート 200MHz に設定した場合で、2.1us の遅延があることが分かります。

USRP-2954 IDL ではFPGA 内部でリサンプル回路があり、その設定を変えることで IQ レートを変化させることができます。

設定によって遅延が変わることが分かりました。

レートを下げると遅延時間も長くなるようです。

まとめ

今回は USRP-2954 (IDLプロジェクト) での処理遅延について計測をしてみました。弊社の簡易的なツールなので、0.1us 程度の分解能ですがオーダー的には遅延量を計測できました。200MHz で 2.1us を長いとみるか、短いとみるかはアプリケーションによって変わると思います。(ショートレンジの通信だと結構きついかもしれませんね。。。)

FPGA のデフォルト回路を簡易化すれば遅延量は短くすることができると思いますし、信号処理を追加すれば遅延は増える方向になると思います。

0 件のコメント :

コメントを投稿