こんにちは、ドルフィンシステムの笹生です。

今回は 「X410 のカスタムFPGA のリソース量を確認」してみたご報告です。

前回紹介した「X410 カスタム FPGA で CWを連続送信する」サンプルで使われている FPGA のプロジェクトを実際にコンパイルして使用リソースを確認してみました。

本記事では以下のページを参考にしておりますので是非御一読されてからご覧いただくと良いと思います。

X410 カスタムの FPGA のプロジェクトを開く

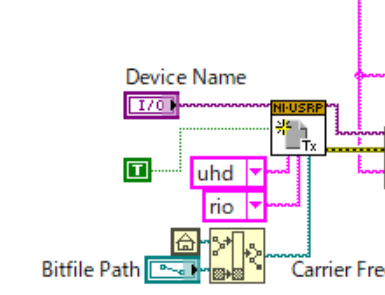

前回紹介したサンプルで指定している X410 の FPGA の Bitfile は、元々コンパイル済みのものを指定しておりました。

現在の所 USRP X410 の開発は従来の USRP-294x, 295x シリーズのようなソフト+FPGAの開発プロジェクトでの提供ではなく、ソフトは NI USRP ドライバ、FPGA は LabVIEW FPGA での開発となるようです。

再掲ですが、上記 URL での解説を読むと、

” <LabVIEW>\instr.lib\niUSRP\ReferenceFPGA”

のパスに FPGA のプロジェクトがあるようなので、別のフォルダにコピーして開いてみます。

実はそのまま持ってくるだけではパスが大部分固定されているため、以下の2つのファイルだけコピーしてくるようにすると良いようです。

・LabVIEW プロジェクトファイル

・Topレベル VI である「Reference FPGA X410.vi」

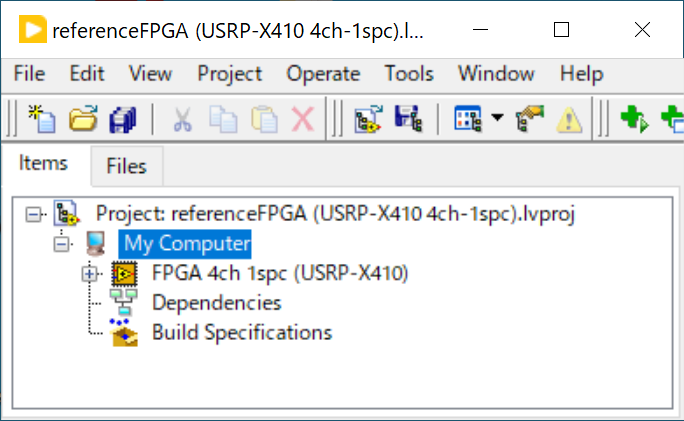

該当フォルダには5つほど LabVIEWプロジェクトファイルがあるのですが、今回は上記 URL にあるように「referenceFPGA (USRP-X410 4ch-1spc).lvproj」と「referenceFPGA (USRP-X410 4ch-4spc).lvproj」の2種類を選んでそれぞれコンパイルしてみました。

・LabVIEW プロジェクトファイル

・Topレベル VI である「Reference FPGA X410.vi」

の2つのファイルをコピーしてきてプロジェクトを開きます。

FPGA の部分を展開すると、コピーした「Reference FPGA X410.vi」がありますが、このパスはコピー元の VI なので一旦プロジェクトから削除して、コピーした「Reference FPGA X410.vi」をプロジェクトに追加します。

(こうすることでコピーしたほうを編集できます。今回は特別編集は行いませんが。。。)

X410 4ch 1spc (100MBW)をコンパイルしてみる

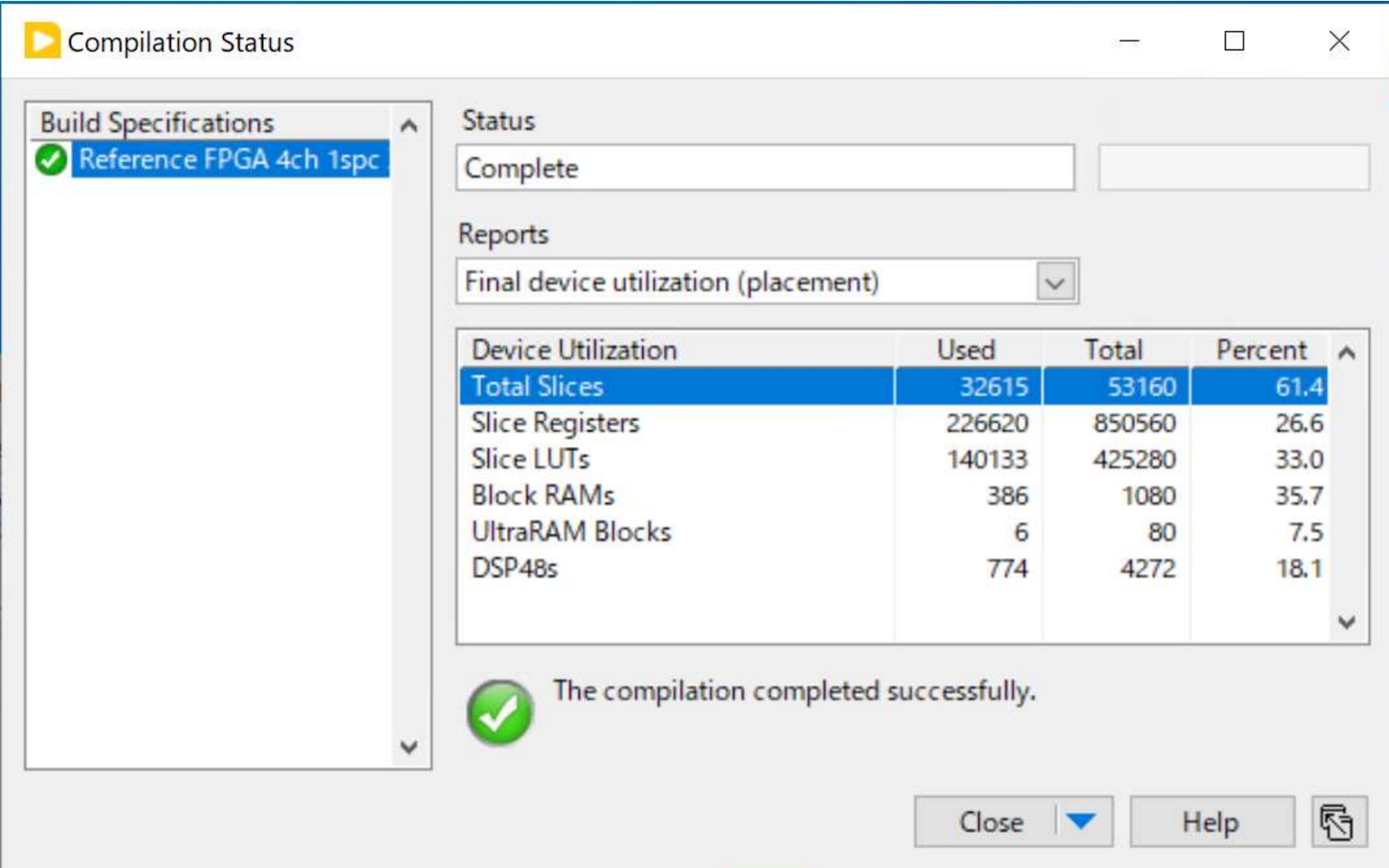

「referenceFPGA (USRP-X410 4ch-1spc).lvproj」の方をコンパイルしてみます。

こちらのプロジェクトは 100M帯域で 4ch 送受信ができるものになります。

FPGA の「Build Specifications」にある「Reference FPGA 4ch 1spc X410」というビルド仕様を右クリックして [Build] をします。

コンパイルが成功しました。

Block RAMs (35.7%) と DSP48s (18.1%) ですので追加回路を入れることも可能そうです。

X410 4ch 4spc (400MBW)をコンパイルしてみる

続いて「referenceFPGA (USRP-X410 4ch-4spc).lvproj」を同じようにコンパイルしてみます。

こちらのプロジェクトは 400M帯域で 4ch 送受信ができるものになります。

残念ながら9時間以上かけて、結果としてコンパイルエラーしました。。。

中間結果の配置結果の時点でかなり Block RAMs (89.6%!) と DSP48s (98.1%!!!) でリソースを消費しているからだと思うのですが、エラーの内容としてはやはり配線が出来なかったようです。

実際には NI 社ではコンパイルが通っているので、オプション調整すれば何とか通るのではないかと思うのですが、これだけ空きリソースが無ければ追加で回路入れることはほとんどできないので、素直にコンパイル済みの Bitfile を使用しましょう。

まとめ

今回は USRP X410 に搭載されている FPGA のデフォルトでの使用リソース量を実際に確かめてみました。まとめると以下のような状況です。

4ch 4spc は既成のビットファイルをおとなしく使用しましょう。

4ch 1spc は空きリソースがあるので信号処理を追加できると思います。

0 件のコメント :

コメントを投稿