皆様こんにちは、ドルフィンシステムの笹生です。

さて、今回は 引き続き LabVIEW FPGA での無線信号処理について解説をしたいと思います。

無線信号処理と言ってもその処理内容は多岐に渡ります。

例えば OFDM のような送信無線信号処理を例に取ると

・符号化

・インターリーブ

・変調

・IFFT

・サイクリックプリフィックス

・フィルタリング

・アップコンバート

など様々な信号処理を経て、ビット列から無線信号へと変換されて送信されます。

ビットを主体とした信号処理から、数値を主体とした信号処理まで多岐にわたるのですが、いずれの処理も FPGA に実装することができます。

FPGA に信号処理を実装するには、FPGA 独特の考え方で設計・プログラミングをしないといけません。

それは、

・1ティック (1クロックサイクル) で動作が完結するようにする

ということです。

このお約束を守らないとコンパイル時にタイミングエラーが起きて、実行することができません。

1 ティックでの処理

そして、その動作を決めるのが SCTL (シングルサイクルタイミングループ) です。

この SCTL ループ内に記述したプログラムは、基本的に1ティック(1クロックサイクル) で動作します。

そのため、この SCTL 内におかれる関数やサブ VI も 1ティックで動作が完結するように記述してあげる必要があります。

そして、SCTL 内のプログラムが 1ティックで終わるか終わらないかは、長時間かかるコンパイルが終了するまで分からないという FPGA 特有の事情があります。

本当にこれは厄介で、FPGA の経験があっても難しいプログラムになってくると、論理的には正しく 1ティックで終わらないというタイミングエラーがコンパイル開始から数時間後に通知されて唖然とすることも良くあります。

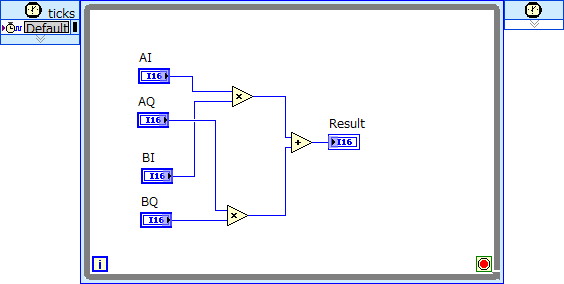

例えば、以下のプログラムはコンパイル可能です。

単純に 4つの整数値を乗算して足すだけのプログラムです。

これを SCTL 内に記述してコンパイルしてみます。

ターゲットは PXIe-7976R とします。

SCTL のクロックがデフォルトの時は 40MHz クロックなのでコンパイルが通ります。

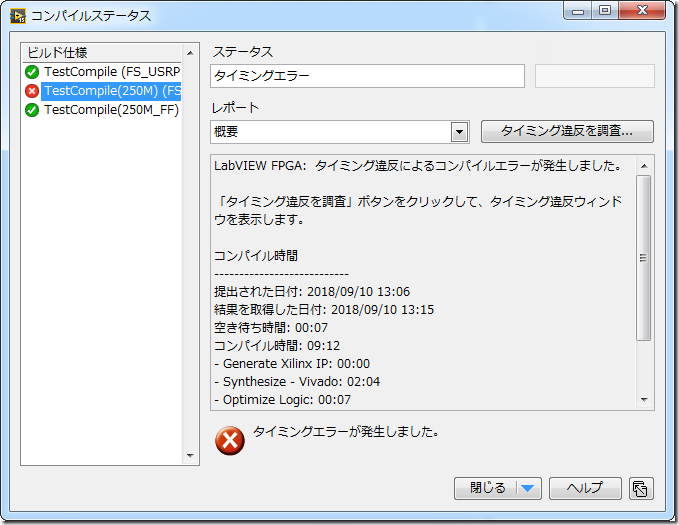

しかし、250MHz といった高速のクロックの場合はコンパイルエラーになってしまいました。

これは乗算して足し算するまでが

・40MHz 1 ティックで終了する処理量なのでコンパイル OK

・250MHz での 1ティックでは終わらない処理量なのでコンパイル NG

だからです。

つまり単純に処理をどんどん増やしていくと高速なクロックで処理させることがだんだんできなくなっていくのです。

ではどうしたら 250MHz 1ティックに間に合わせることができるでしょうか?

高速なクロックでコンパイルを通すには。。。

答えは「フィードバックノードを途中に入れる」です。

実はこの「フィードバックノードを途中に入れる」ことで、高速なクロックで処理させることが可能になります。

実際、以下のようにフィードバックノードを各所に入れると 250MHz のクロックでコンパイルが OK になります。

なぜか?

なぜフィードバックノードを途中に入れると高速なクロックで処理させることができるかについては次回解説したいと思います。

フィードバックノードは物理的な意味合いもあるので、次回じっくり解説したいと思います。

![clip_image001[4] clip_image001[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEhEUoDHB35_vXBqMUE_U1EExW5yUgkVznIZI_zgmgLrRHNd_yV3F1HR2ZP2-dNV7Bbb5xIyC5MhLhNm5pBCx3hWBt9SkiEFw5rM57xhTK9I3A09QhyphenhyphenFdMH7UyD7euGDPtdVAlfOXZwMkuFn/?imgmax=800)

![clip_image002[4] clip_image002[4]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEiotJIDXkgm5J1wXq7tgNLvrYtJGFZv2Wni0C7xYfwBFQdWobqhIcRrIlGeN4DHLM3EHEokv_Dy5fDwLjzBgo6fe9CibemNsSa1R_zvaUt_pYtMSP4dsD4j18W8_kHNYHsVPZZLxZ3hETiH/?imgmax=800)

0 件のコメント :

コメントを投稿