今回皆様と共有したい情報は、

「SDR データ取得の一番先頭は少し0データになる(DDC のフィルタ遅延)」

です。

これはどういうことかといいますと、SDR (ここでは USRP-RIO、FlexRIO+5791 などの IDLとします)で取得開始した直後の受信 IQ データには、0 が数十サンプル挿入されるという現象です。

(※IDL = Instruments Design Libraly、National Instruments社から提供されている開発サンプル)

■この現象が起きる原理

この現象がおきるのは FPGA 内の DDC (デジタルダウンコンバータ) で使用されているフラクショナルデシメータのアンチエイリアスフィルタの遅延が原因です。

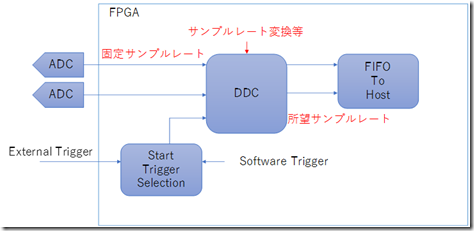

<IDL のADC から ホストへの FIFO へのデータ転送の簡略図>

IDL ベースの SDR 受信機では、固定サンプルレートの ADC の後に、FPGA 内部で DDC をして所望のサンプルレートにしています。

よーいドンでスタートトリガ(外部またはソフトウェアのトリガ)をかけて、回路がいっせいに動き出すのですが、この FPGA 内部の DDC での「アンチエイリアスフィルタ」(FIRフィルタと思われる)の遅延分があり、最初の数十サンプルがフィルタタップの初期値である 0 が出力されるようです。

残念ながら DDC 内部で使用されている回路を内部まで見ることができませんが、恐らくそういうことだと思います。

実際に、DDC 内部で使用されている「フラクショナルデシメータ」のヘルプにアンチエイリアスフィルタの群遅延についての記述があります。

Group delay of the anti-alias filter

decimation factor <= 16: group delay = 15 output samples

16 < decimation factor <= 128: group delay = (256 / decimation factor) + 15 output samples

128 < decimation factor <= 2,048: group delay = (2,056 / decimation factor) + 15 output samples

2,048 < decimation factor <= 32,768: group delay = (34,624 / decimation factor) + 15 output samples

32,768 < decimation factor <= 65,536: group delay (65,344 / decimation factor) + 15 output samples

貼り付け元 <http://zone.ni.com/reference/en-XX/help/374500C-01/oscopes/idl_dsp_fpga/>

遅延量(group delay)は ADC の固定サンプルレートと、設定したDDC サンプルレートの比であるデシメーションファクターによって決まります。

■遅延を計算と実機計測で確認

実際に、USRP-RIO IDL と、NI 5791+FlexRIO IDL での遅延を計算、実機で計測をしてみました。

入力信号には分かりやすく連続した正弦波 CW をいれています。

上記計算よる遅延量(DF:decimation factor, delay:groupe delay)

|

|

USRP-IDL(USRP-2954) |

NI5791+FlexRIO |

|

ADC サンプル周波数 |

200M |

130MHz |

|

100MS/s 設定 |

DF=2, delay=15 |

DF=1.3, delay=15 |

|

10MS/s 設定 |

DF=20, delay=27.8 |

DF=13, delay=15 |

|

1MS/s 設定 |

DF=200, delay=25.28 |

DF=130, delay=30.82 |

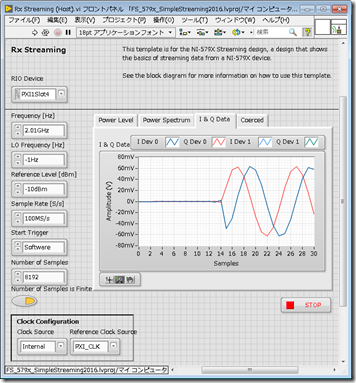

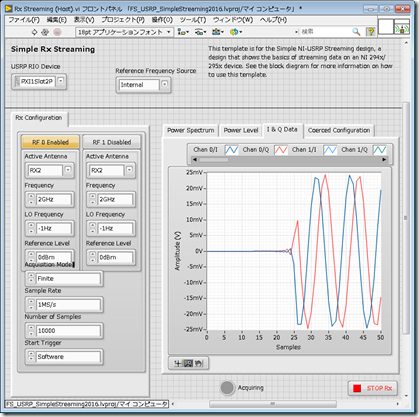

実測:USRP-IDL 100MS/s 設定では概ね 15 サンプル遅延で正弦波が出力

実測:NI-5791FlexRIO-IDL 100MS/s 設定では概ね 15 サンプル遅延で正弦波が出力

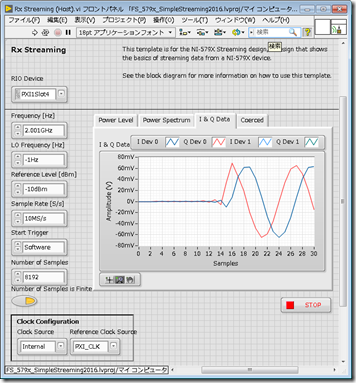

実測:USRP-IDL 10MS/s 設定では概ね 28 サンプル遅延で正弦波が出力

実測:NI-5791FlexRIO-IDL 10MS/s 設定では概ね 15 サンプル遅延で正弦波が出力

実測:USRP-IDL 1MS/s 設定では概ね 26 サンプル遅延で正弦波が出力

実測:NI-5791FlexRIO-IDL 1MS/s 設定では概ね 31 サンプル遅延で正弦波が出力

実測でも計算値とほぼ一致する結果になりました。

ちなみに取得モードを「Continuous(連続)」にしていれば、スタートトリガをかけた先頭だけ 0 が入ります(遅延します)があとは連続しています。取得モードを「Finite(有限)」にした場合は都度スタートトリガをかけるのと同じなので毎回取得の先頭に 0 (遅延)が入ります。

一定間隔でデータをとりたいが毎回先頭に 0 が入るのを避けたい場合には、取得モードを「Continuous(連続)」にして FPGA 内部でデータを切り出してあげる改造をすることで対応できます。これでも本当に一番最初だけは 0 が入ってしまいますが、あとは常に連続しているのを切り出すことで、「Finite」とは異なり、2回目の取得以降の先頭に 0 が入ることはありません。

IDL の場合、FPGA の改造ができるので、ある程度トリガとデータ取得の関係もある程度思ったとおりの制御をさせることは可能です。

0 件のコメント :

コメントを投稿